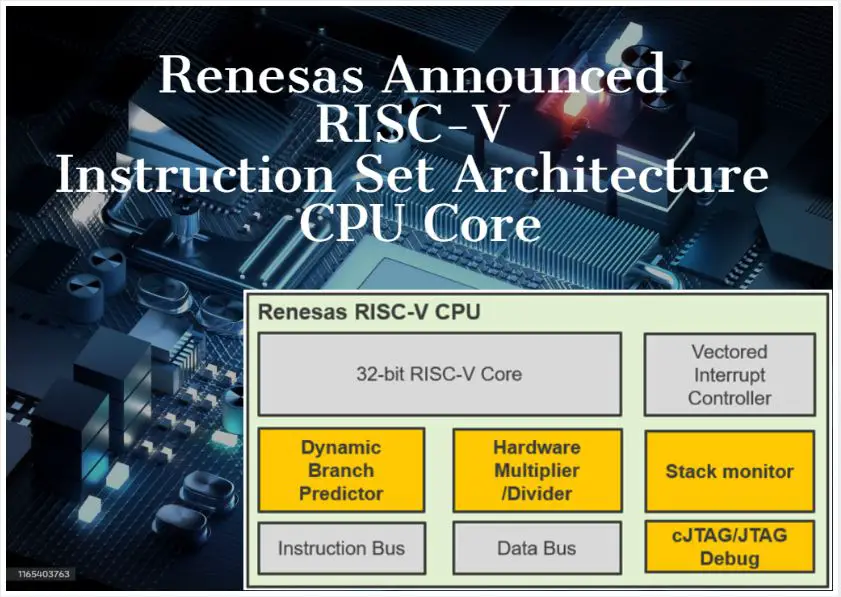

Renesas Electronics Corporation, a leading semiconductor solutions provider, announced the successful design and testing of a 32-bit CPU core utilizing the open-standard RISC-V instruction set architecture (ISA). This marks Renesas as one of the pioneering entities to independently develop a CPU core for the 32-bit RISC-V market, presenting a versatile platform for various sectors such as IoT, consumer electronics, healthcare, and industrial systems.

The newly crafted CPU core boasts an impressive 3.27 CoreMark/MHz performance, surpassing comparable architectures in the market. Detailed insights into its architecture reveal extensions to enhance performance while minimizing code size, underscoring its technical superiority.

With plans to sample devices and launch RISC-V-based MCUs in Q1 2024, Renesas anticipates a transformative impact on its MCU leadership and the semiconductor industry. The ripple effects of this innovation are poised to redefine industry standards and expectations.

The adoption of RISC-V by Renesas heralds a new era of versatility. The architecture’s flexibility, scalability, power efficiency, and open ecosystem position it ideally for IoT, consumer electronics, healthcare, and industrial systems, amplifying its relevance across diverse sectors.

The RISC-V instruction set architecture (ISA) has gained remarkable traction within the semiconductor industry, heralding a new era of innovation and unprecedented flexibility for designers. Renesas, having previously embraced RISC-V technology with 32-bit ASSP devices for voice and motor control, has taken a significant leap forward with the creation of its in-house engineered CPU core, a pioneering advancement within the domain.

This groundbreaking CPU core is a versatile marvel, designed for a multitude of applications. It can function as a primary CPU, manage on-chip subsystems, or seamlessly integrate into specialized ASSP devices. Renesas’ implementation stands out for its efficient use of silicon area, minimizing operational and leakage currents, and effectively reducing costs while delivering robust performance even in deeply embedded applications.

At its core, the CPU provides implementers with the flexibility to choose between the RV32 ‘I’ or ‘E’ options, optimizing the number of general-purpose registers. For instance, in scenarios requiring dedicated peripheral servicing or housekeeping tasks within small subsystems, this flexibility proves invaluable.

Renesas’ integration of specific RISC-V ISA extensions further enhances functionality. The ‘M’ extension optimizes multiplication and division operations, leveraging hardware units for faster execution. ‘A’ extension supports atomic access instructions, essential for concurrency and exclusive access management in RTOS-based systems. ‘C’ extension defines compressed instructions, conserving memory space and enhancing performance. ‘B’ extension adds instructions for bit manipulation, ideal for managing peripheral registers and protocols based on bitfield encoded values.

The elegance of the RISC-V ISA lies in its customizable nature, allowing designers to optimize power consumption, performance, and silicon footprint based on their specific requirements. Renesas’ CPU includes a stack monitor register, crucial for detecting and preventing stack memory overflows, ensuring the integrity of systems and mitigating runtime issues.

The CPU’s dynamic branch prediction unit optimizes processing efficiency in systems with multiple decision paths, loops, and branches, enhancing overall code execution throughput.

Furthermore, Renesas has fortified the CPU with advanced debug capabilities, including support for compact JTAG interfaces and performance monitor registers. Additionally, a register bank save function bolsters responsiveness to events, crucial in achieving hard real-time behavior in deeply embedded devices.

For application verification and benchmarking, the CPU integrates an efficient instruction tracing unit, offering insights into runtime behavior.

To support developers, Renesas has ensured the availability of necessary toolchains and validated the CPU’s features through real silicon product implementation. Initial benchmarks showcasing a 3.27 CoreMark/MHz performance using an LLVM-based compiler toolchain demonstrate its superiority over comparable architectures. Renesas’ commitment to providing a comprehensive RISC-V-based MCU portfolio underscores its readiness to cater to diverse customer needs, amplifying their innovative strides in the semiconductor landscape.

Author Profile

- 20+ years embedded hardware design professional with a burning passion for teaching. Sharing the intricate world of embedded hardware is my mission and joy.

Latest entries

Tech Updates30 November 2025STM32WBA6: The Next-Generation MCU Powering Secure Short-Range Wireless Designs

Tech Updates30 November 2025STM32WBA6: The Next-Generation MCU Powering Secure Short-Range Wireless Designs Blogs24 November 2025High-Speed PCB Layout Design Guide-104

Blogs24 November 2025High-Speed PCB Layout Design Guide-104 Tech Updates14 September 2025Renesas Launches RL78/L23 Ultra-Low-Power MCUs to Power Smarter Home Appliances

Tech Updates14 September 2025Renesas Launches RL78/L23 Ultra-Low-Power MCUs to Power Smarter Home Appliances Blogs7 September 2025High-Speed PCB Layout Design Guide-103

Blogs7 September 2025High-Speed PCB Layout Design Guide-103